<aside> 💡

友安昌幸 - 合同会社アミコ・コンサルティング

</aside>

<aside> 💡

<リード文>

</aside>

半導体産業は現在、AIチップ革命という大きな転換点を迎えています。従来の汎用プロセッサから、AI処理に特化した専用チップへの移行が急速に進んでいます。この変化は単なる技術進化にとどまらず、産業構造そのものを変革する大きなうねりとなっています。

AIチップとは、機械学習やディープラーニングなどのAI技術に特化した半導体チップのことです。従来の汎用プロセッサと比較して、AI処理を効率的に行うための並列処理能力や特殊な演算ユニットを備えています。

市場調査によれば、AIチップ市場は今後も急速な成長が見込まれています。特にデータセンターや自動運転車、スマートフォンなど、AIの活用が進む分野での需要が拡大しています。この成長を支える要因として、AIの普及拡大、5GやIoT技術の進展、そして半導体供給網の改善が挙げられます。

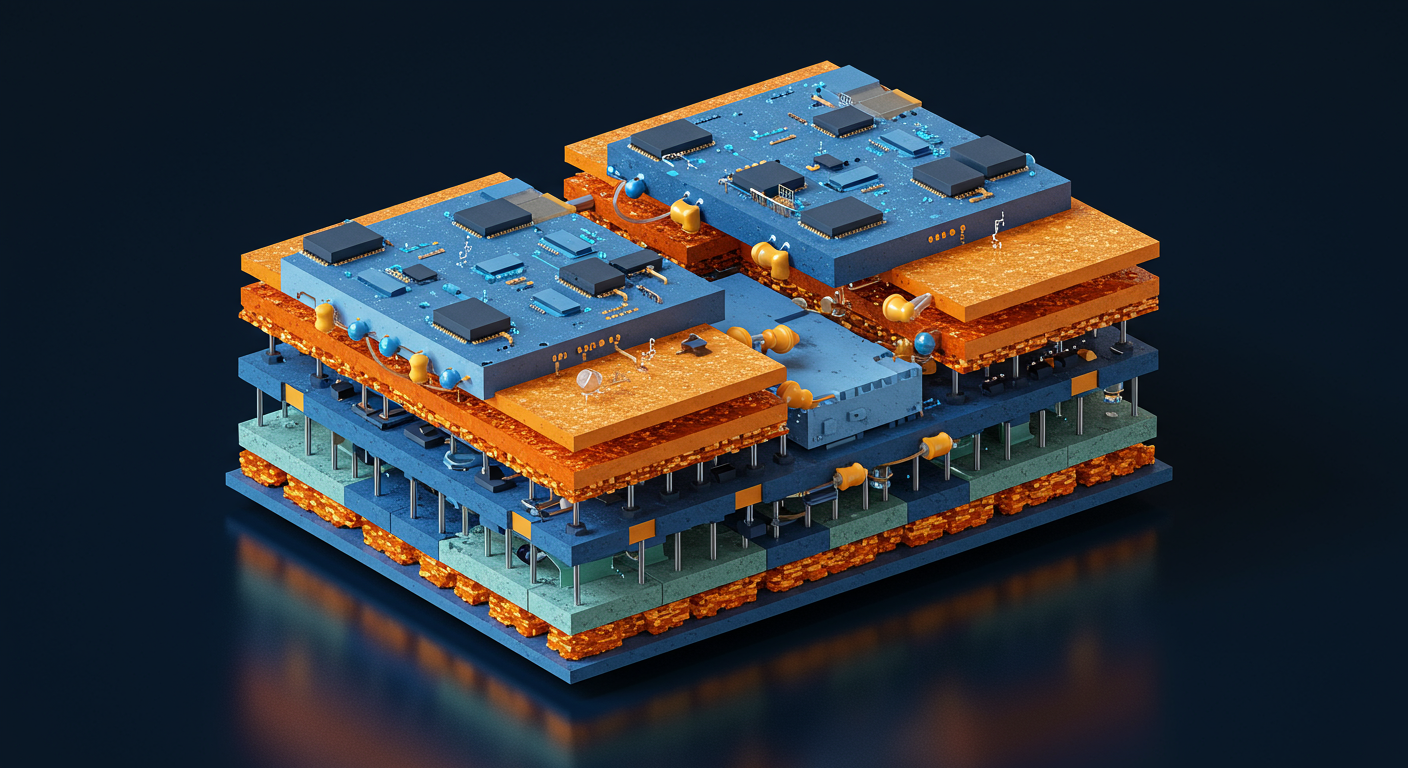

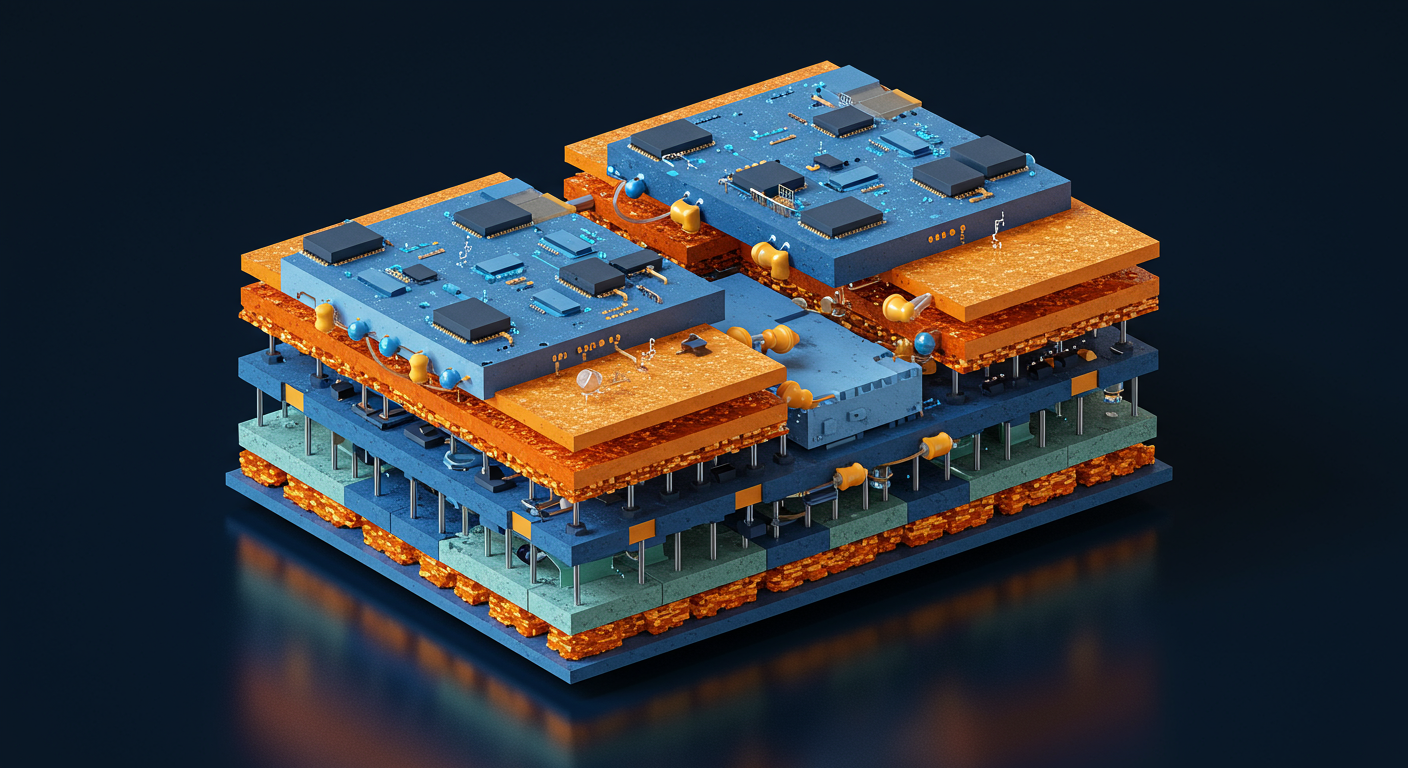

AIチップの性能向上を支える重要な技術として、高層3Dチップ製造技術が注目されています。マサチューセッツ工科大学(MIT)のエンジニアたちが開発したこの技術は、半導体層を直接積み重ねることで、より高密度で効率的なチップ製造を可能にします。

従来のチップ製造では、シリコンウェハー上に半導体層を形成し、その上にトランジスタを配置する方法が主流でした。しかし、このアプローチではシリコンウェハーの厚みが多層構造の制約となり、チップの性能向上に限界がありました。

MITの技術は、この制約を打破するものです。シリコンウェハーに依存することなく、高品質な半導体層を直接他の層の上に積層することで、トランジスタの密度を飛躍的に向上させます。この技術により、従来よりも多くの機能をより小さな面積に集約することが可能となります。

この高層3Dチップ技術の最も注目すべき点は、トランジスタ密度の向上、エネルギー効率の改善、設計自由度の拡大という3つの利点です。特にAIハードウェアにおいては、演算速度とエネルギー効率を同時に高められる点で、次世代AIシステムの基盤となる可能性を秘めています。

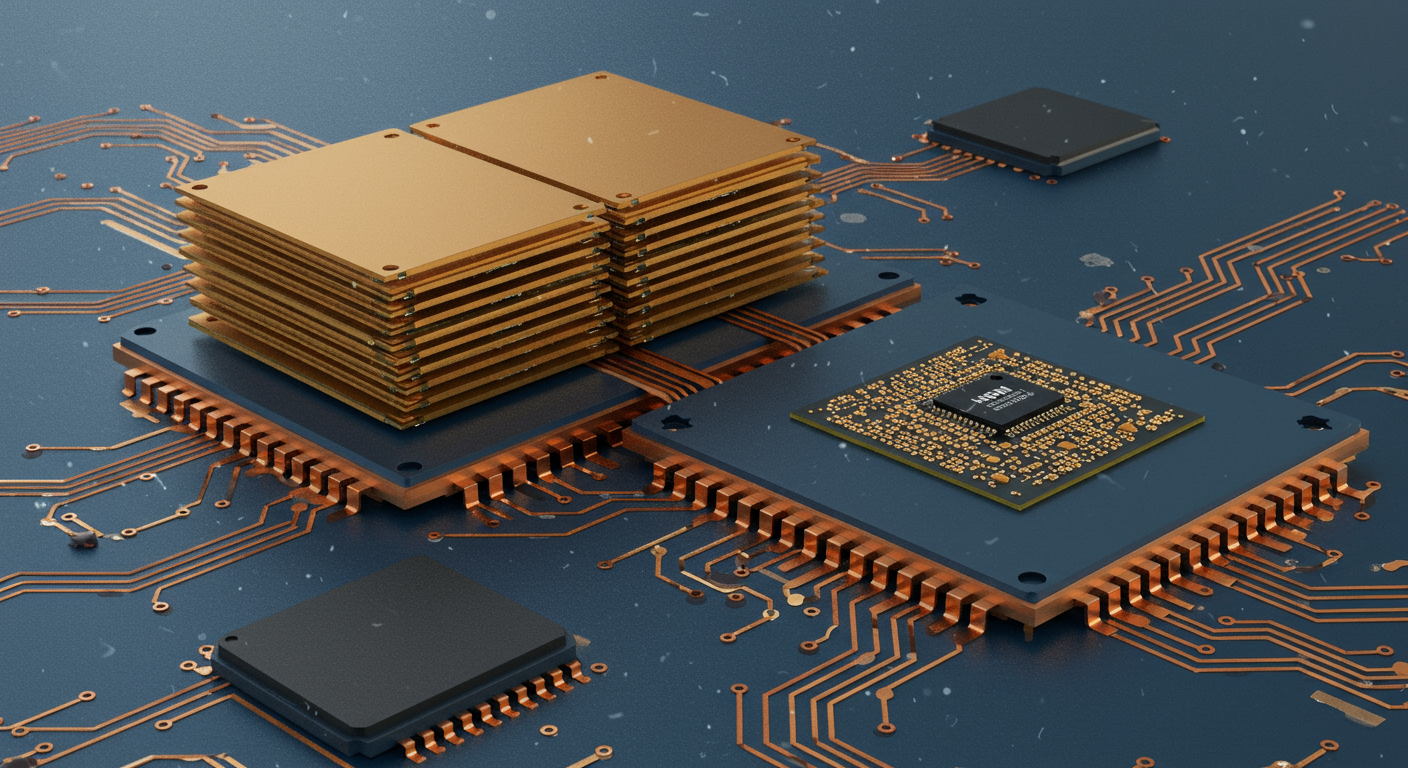

AIチップの性能を大きく左右する重要な要素として、メモリ帯域幅の問題があります。この課題を解決する技術として注目されているのが、HBM(High Bandwidth Memory)です。HBMは非常に高い帯域幅(データ転送速度)を持ったDRAMであり、AIチップの処理能力を最大限に引き出す役割を担っています。

従来のDDR(Double Data Rate)タイプのDRAMと比較して、HBM第2世代では伝送速度2Gbpsでバス本数が1024本、帯域幅254ギガバイト/秒と高い伝送速度と非常に多くのバス本数を両立し、高帯域幅を実現しています。

HBMが高い伝送速度と多くのバス本数を実現できる理由は、TSV(Through-Silicon Vias)を使用した高密度配線と垂直方向のメモリ積層にあります。従来のワイヤーボンド接続と比較して高密度な配線が可能となるとともに、配線距離が短くなることにより、信号の伝播遅延が減少し、高い動作周波数を実現しています。

また、3次元構造を生かして、メモリダイの下にロジック層を配置接続することにより、メモリの操作制御およびデータ転送の効率化が可能となっています。HBMは単独のパッケージでは存在せず、ホストプロセッサと組み合わせたマルチチップパッケージの形状で製品となります。